Это первая часть цикла посвященная программируемой логике и среде разработки Quartus компании Altera. В ней разбирается процесс получения дистрибутива бесплатной редакции IDE Quartus. А также процесс создания нового проекта в данной среде.

Следующая часть цикла: ПЛИС Altera. Часть 2: проектирование цифровой схемы.

Во второй части разбирается процесс добавления к проекту новых файлов. Визуальное проектирование цифровой схемы.

Данный цикл статей ориентирован на работу с платой CTRL-CPLD-EPM570 на чипе Altera Max II. Эта плата не является строго необходимой для успешного освоения материала, так как описываемый в нем проект не использует каких-то специальных возможностей Max II.

Для загрузки проекта в микросхему используется недорогой программатор совместимый c Altera USB Blaster.

Шаг 1. Получение дистрибутива Altera Quartus

Внимание! В 2015 году Altera была приобретена компанией Intel. Бренд Altera прекратил существование в июле 2018 года, адрес сайта altera.com теперь никуда не ведет. Новое имя Altera – Intel Programmable Solutions Group (PSG). Вся документация и ПО необходимые для работы с ПЛИС Altera теперь доступны на сайте intel.com

Для создания проектов под ПЛИС Altera используется фирменная IDE - Quartus. Версий Quartus существует бесчисленное множество, и требуется выбрать правильную под имеющуюся микросхему. Altera регулярно выкидывает поддержку старых чипов из новых версий своего ПО. В свою очередь, в новых версиях Quartus меняются требования к программному и аппаратному обеспечению компьютера. Например, Quartus 13.1 является последней версией работающий как 64‑х так и 32‑х разрядных системах.

Данная серия статей ориентирована на Quartus версии 13.1. Так как с одной стороны, он не имеет специальных требований к разрядности операционной системы. С другой - он поддерживает микросхемы серии MAX II.

Для получения дистрибутива Quartus необходимо иметь аккаунт на сайте intel.com или intel.ru К сожалению, в настоящее время (в декабре 2018 года) процедура регистрации на сайте Intel несколько затруднена. Форму регистрации отыскать непросто. На нее можно выйти только на заключительном этапе загрузки дистрибутива. Также, в процессе регистрации Вам понадобится предоставить действующий адрес электронной почты, номер сотового телефона и обязательно придумать сложный пароль.

Пока идет активный процесс слияния Intel и Altera лучше воспользоваться сторонними ресурсами для загрузки Quartus. Дистрибутив выложен в общий доступ на Yandex‑диск, ссылка для загрузки: https://yadi.sk/d/bcrz7IAAKY6dQg

Для работы с микросхемой MAX II потребуется сам Quartus, и пакет для поддержки MAX II и MAX V. Это файлы «QuartusSetupWeb-13.1.0.162.exe » и «max_web-13.1.0.162.qdz » соответственно.

В конце статьи доступна и старая версия инструкции по загрузке дистрибутива: . По ней можно получить примерное представление о том, как загрузить дистрибутив с сайта intel, так как на сайте Intel используется Software Selector от Altera. И также как у Altera, Software Selector перенаправляет пользователя на страницу входа при попытке скачать любой файл, в случае если пользователь предварительно не зашел на сайт со своей учетной записью.

Данная страница входа - единственное место, которое содержит ссылку на форму регистрации на сайте Intel. Ссылки для регистрации располагаются в правой части страницы. Для рядовых пользователей можно использовать ссылку «Register now for an individual account ». Ссылка обозначена на рисунке ниже.

Шаг 2. Установка Quartus II Web Edition 13.1

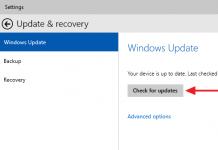

Установка САПР Quartus II не таит каких‑либо сюрпризов и проходит по отработанному алгоритму «Next → Next → Finish».

Параметры установки изменять не требуется. В дальнейшем предполагается что Quartus II был установлен с параметрами по умолчанию.

По окончании установки среда Quartus запустится автоматически. Этот автозапуск активирован по умолчанию.

При первом запуске САПР Quartus будет предложено настроить отправку телеметрии в Altera (здесь это называется TalkBack) и выбрать тип лицензии.

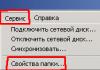

Отключение или включение «TalkBack» задается галочкой «Enable sending TalkBack data to Altera», которая доступна и после установки Quartus через меню Tools → Options → Internet Connectivity → кнопка «TalkBack Options…».

При запросе типа лицензии необходимо просто выбрать второй пункт: «Run the Quartus II software». Таким образом Вы выберете бесплатную лицензию.

На этом установка и первичная настройка ПО завершена и можно переходить к созданию своего первого проекта.

Шаг 3. Quartus II — создание первого проекта

Первым делом создайте папку для нового проекта. Назовите ее «firstproject».

Внимание! Путь до директории проекта не должен включать кириллических символов! С поддержкой кириллицы у Quartus II 15 и 13 версии имеются проблемы. Другие версии не тестировались.

Теперь запустите Quartus II. При запуске свежеустановленного Quartus II Вас встретит окно, вид которого представлен ниже.

Для создания нового проекта воспользуйтесь мастером доступным по кнопке «New Project Wizard» или через меню File → New Project Wizard.

При запуске мастера будет выведено окно, в котором представлено краткое перечисление параметров проекта, настраиваемых в процессе работы мастера.

Нажмите «Next» и будет выполнен переход к окну представленном на скриншоте ниже. В этом окне необходимо указать рабочую директорию («What is the working directory for this project?») и название всего проекта в целом («What is the name of this project?»). А также имя его главного модуля («What is the name of the top-level design entity for this project? …»).

В качестве имени главного модуля мастер автоматически подставляет название проекта и это общая рекомендация для проектов в Quartus II, от которой не стоит отклоняться без реальной необходимости.

Пара слов о самом «главном модуле». Проект Quartus II может включать в себя множество файлов (модулей) описывающих различные функциональные блоки проектируемой интегральной схемы. И среди этого множества обязательно выделяется один файл, в котором описываются взаимосвязи между всеми блоками схемы - top‑level design entity. Для небольших проектов, содержащих всего один файл, этот единственный файл будет являться и главным модулем проекта.

На следующем шаге мастер предложит добавить в новый проект файлы из каких-либо ранее созданных проектов. Так как это первый Ваш проект, то просто перейдите к третьему шагу.

Третий шаг один из самых важных. Здесь необходимо указать конкретную модель используемой Вами микросхемы ПЛИС. Окно мастера на данном шаге представлено на скриншоте ниже. В этом окне доступно множество параметров для поэтапного отбора необходимой микросхемы из обширного списка доступных. Начать лучше всего с блока «Device Family». Здесь нужно выбрать семейство к которому относится Ваш чип. На плате CTRL-CPLD-EPM570 установлен чип EPM570T100C5N, который относится к семейству Max II.

В блоке справа – «Show in ‘Available devices’ list», можно настроить фильтр для сокращения перечня микросхем, который располагается в нижней части окна. Можно указать тип корпусировки микросхемы. Количество выводов ее корпуса. А также скорость работы ядра в условных единицах. Предпоследним идет фильтрация по названию микросхемы. Удобнее всего будет использовать именно её, так как название микросхемы уже точно известно. Но по маркировке EPM570T100C5N никаких микросхем к выбору не предлагается. Сократите название до EPM570T100C5, и выберите в появившемся списке микросхему с этим названием как ближайшую совместимую.

Если обратится к даташиту, то выяснится что последняя буква N в маркировке микросхемы обозначает лишь отсутствие свинца в упаковке чипа. Данный факт не имеет значения для Вашего проекта в Quartus II так как ядро у EPM570T100C5N и EPM570T100C5 абсолютно идентично.

Перейдите к следующему, четвертому шагу – «EDA Tool Settings». Здесь можно настроить интеграцию с различными средствами автоматизированного проектирования от сторонних разработчиков, которые используются профессиональными проектировщиками микросхем. Так как целью этой статьи является помощь в освоении САПР Quartus II, а не целого пакета приложений стоимостью многие тысячи долларов, то просто перейдите к заключительному шагу.

На последнем шаге выводится обобщенный список параметров Вашего нового проекта. Проверьте чтобы были верно заданы такие параметры как: имя и рабочая директория проекта, top-level design entity, маркировка используемой микросхемы. После чего нажмите кнопку «Finish». На этом все! Проект создан.

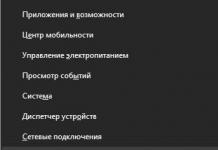

Возможно, Вы обратили внимание что кнопка «Finish» доступна для нажатия уже с первого шага мастера. И ее действительно можно нажать уже на первом шаге, задав только рабочую директорию, имя проекта и главного модуля. Только эта информация является абсолютно необходимой для создания нового проекта. Все остальные параметры доступны для настройки в любое время, из главного меню программы. Так, чтобы добавить еще файлов в свой проект (второй шаг мастера) используйте меню Project → Add/Remove Files in project. Для выбора или изменения модели микросхемы под которую создается проект (третий шаг мастера) используйте меню Assignments → Device. Интеграция с дополнительными инструментами разработки (предпоследний шаг мастера) – это Assignments → Settings → EDA Tool Settings.

Вообще, все настройки проекта собраны в окне, вид которого представлен на скриншоте ниже. Окно вызывается через меню Assignments → Settings.

Пункт Files – именно это окно вызывается и из главного меню программы (Project → Add/Remove Files in project). EDA Tool Settings – аналогично. Выбор микросхемы доступен по кнопке «Device…» в правом верхнем углу окна настроек проекта.

На этом первая часть статьи по обучению работе с ПЛИС компании Intel (Altera) завершается.

(Архив) Получение дистрибутива Altera Quartus

Для получения дистрибутива Quartus зайдите в свой аккаунт myAltera на сайте altera.com: кнопка «LOG IN» в правом верхнем углу сайта, рядом со строкой поиска.

Если у Вас еще нет аккаунта myAltera, то Вы можете создать его просто перейдя по ссылке в самом низу формы регистрации, строка «Don’t have an account? Create one».

После входа в myAltera перейдите в центр загрузки сайта . Ссылка на момент написания: https://www.altera.com/downloads/download-center.html

Если ссылка окажется нерабочей, то перейдите в центр загрузки через домашнюю страницу своего аккаунта . Для этого выберите раздел «SUPPORT » и в нем перейдите по ссылке «Downloads », которая и приведет Вас в центр загрузки.

В центре загрузки есть прямые ссылки на загрузку последней версии Quartus

в различных редакциях. Ниже располагается блок «Software Selector

», прокрутите страницу до него.

В центре загрузки есть прямые ссылки на загрузку последней версии Quartus

в различных редакциях. Ниже располагается блок «Software Selector

», прокрутите страницу до него.

В

Software Selector реализовано несколько способов выбора необходимо

го

дистрибутива Q

uartus, вкладки: «

Select by Version»

(прямой выбор по

требуемой

версии ПО

), «

Select by Device»

(выбор версии ПО по наличию поддержки конкретной микросхемы

), «

Select by Software» (выбор программного продукта

по

его названию

).

В

Software Selector реализовано несколько способов выбора необходимо

го

дистрибутива Q

uartus, вкладки: «

Select by Version»

(прямой выбор по

требуемой

версии ПО

), «

Select by Device»

(выбор версии ПО по наличию поддержки конкретной микросхемы

), «

Select by Software» (выбор программного продукта

по

его названию

).

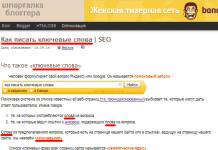

Наиболее удобным вариантом представляется выбор по наличию поддержки имеющейся микросхемы.

Например, если используется микросхема Altera Max II , то необходимо выбрать вкладку « Select by Device», и в блоке « Devices» раскрыть пункт « MAX series». В появившемся списке выбрать Max II .

Справа от блока Devices будет выведен

список редакций и версий Quartus

включающих поддержку Max II

.

Бесплатной редакцией является только Web Edition.

Справа от блока Devices будет выведен

список редакций и версий Quartus

включающих поддержку Max II

.

Бесплатной редакцией является только Web Edition.

При выборе версии обратите внимание на тот факт, что Quartus II начиная с версии 14.0 работает только в 64‑битных системах. По этой причине рекомендую остановится на Quartus II 13.1. Далее будет описана работа и процесс установки именно для тринадцатой версии.

После выбора версии Вы перейдете на страницу параметров загрузки дистрибутива Quartus II Web Edition.

«Operating System» - Windows.

« Download Method » выбирайте по своему усмотрению. Отличие «Akamai DLM3 Download Manager» от « Di rect Download» в том, что в первом случае перед загрузкой файлов самого Quartus нужно будет сначала загрузить и запустить дополнительное приложение под ОС Windows. Это приложение позволяет выбрать к загрузке одновременно несколько файлов, а также поддерживает их докачку. При выборе режима загрузки « Di rect Download» файлы можно будет загружать отдельно, каждый по своей ссылке, силами Web-браузера.

На скриншоте выше выбран вариант загрузки « Di rect Download» .

Загрузите файлы «Quartus II Software » и «MAX II, MAX V device support ». Это необходимый минимум для работы с микросхемой MAX II .

ВВЕДЕНИЕ

Обычно, когда кто-то видит функционирующую плату, всегда задают одни и те же вопросы: - Это Ардуино? - А как это работает без Ардуино?

Это не микроконтроллер, это даже не процессор, это ПЛИС. ПЛИС - это программируемая логическая интегральная схема , такая микросхема состоит из множества одинаковых блоков или макроячеек, каждый производитель по своему их называет, так у Xilinx это Slices (ломтики) у Altera - LogicElements (логические элементы). Эти блоки относительно простые, они могут выполнять роль нескольких логических элементов, быть маленькой таблицей поиска (LUT), содержать готовый сумматор, умножитель, блок цифровой обработки сигналов (DSP), в общем все что задумает производитель. Пользователь может по своему желанию расположить и настроить эти блоки как ему захочется, реализовав таким образом достаточно сложные цифровые схемы. На ПЛИС можно реализовать хоть микроконтроллер, реализовав например ту же Ардуино или процессор вашей собственной архитектуры, например не регистровый а стековый процессор, даже свою собственную ПЛИС можно реализовать на ПЛИС!

Из доступных бюджетных ПЛИС можно выделить двух основных производителей Altera и Xilinx, с их продукции можно начать свой путь освоения данных технологий. На мой взгляд лучше выбрать чипы компании Altera, так как их среда проектирования стабильно обновляется, а выбрав один популярный чип Xilinx XC3S500E вам придется довольствоваться устаревшей средой ISE 14.7 (хотя и там есть свои плюсы).

В иностранной литературе можно встретить сокращения для ПЛИС: FPGA и CPLD. CPLD (Complex Programmable Logic Device) - чипы с небольшим числом макроячеек, специализированных блоков и малым энергопотреблением. Большой проект не получится синтезировать для такого типа чипов, но и для них находят применение на практике, так у редкого микроконтроллера найдется, скажем 300 ножек. Такие чипы часто применяют в качестве интерфейсных систем, предобработчиков, расширителей ввода-вывода. FPGA (Field-Programmable Gate Array) - программируемая пользователем вентильная матрица (ППВМ), значительно более мощные чипы по сравнению с CPLD, но потребляющие больше энергии и стоящие значительно дороже. Для уменьшения затрат площади кристалла FPGA чипы могут содержать уже готовые функции, такие как блоки цифровой обработки сигналов (DSP блоки), встроенные процессоры, встроенная память. FPGA широко применяются для проверки и верификации проектов, в так называемой докремниевой проверке пригодности, тем самым уменьшая затраты и время перед выходом продукта. FPGA чипы могут быть переконфигурированы практически в любой момент времени, сейчас ведутся разработки, например в Intel, по совмещению архитектур обычного процессора и чипа FPGA. У Xilinx уже есть такие решения - Zynq, но о них мы пока не будет вести речь.

Разговор пойдет о более простых вещах, тем более ко мне в руки попал набор разработчика: Cyclone IV 4 FPGA Core Board и Altera USB Blaster Downloader PLD Development kit за 35$, приобретенный на AliExpress .

1 Демоплата Cyclone IV 4 FPGA Core Board, краткая характеристика

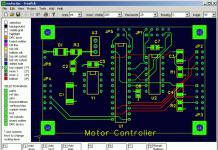

Рис. 1 - Демоплата Cyclone IV 4 FPGA Core Board

На плате (Рис. 1) установлен чип EP4CE6E22C8N, его характеристики:

| Вид ресурса | Краткое описание | Количество |

|---|---|---|

| Logic elements (Les) | Число логических блоков - ячеек, основная характеристика, по которым мы можем сравнивать «мощность» чипов, любая синтезированная логика будет затрачивать данные блоки | 6,272 |

| Embedded memory (Kbits) | Встроенной памяти, пока для нас не важная характеристика | 270 |

| Embedded 18x18 multipliers | Встроенных аппаратных умножителей, очень важный параметр в цифровой обработке сигналов, вся мощь ПЛИС раскрывается, когда несколько умножителей работают параллельно | 15 |

| General-purpose PLLs | Узлов фазовой автоподстройки частоты, пока не важная характеристика, упрощает синхронизацию устройств, работающих на разных частотах | 2 |

| Global Clock Networks | Количество частотных доменов, пока не важная характеристика | 10 |

| User I/O Banks | Число раздельных пользовательских банков ввода-вывода, пока не важная характеристика | 8 |

| Maximum user I/O | Число пользовательских пинов ввода-вывода, мы можем подключить любые устройства, как например к Ардуино | 91 |

На плате установлено:

- Флэш память – при подаче питания ПЛИС будет сконфигурирована в реализацию во флеш памяти. Вы можете синтезировать свой проект и записать в эту флэш

- Кварц 25 Мгц – генератор опорной тактовой частоты, именно на этой частоте будут работать все наши проекты, наша ПЛИС может поддерживать до 10 таких каналов.

- Светодиоды – 10, кнопки – 2.

- Пины ввода-вывода 61 + 2 земля, 1 не соединен. Можно подключить разнообразные устройства. ЦАП-АЦП, акселерометры и гироскопы, символьный и графические дисплеи, как и у Ардуино.

- Питание через USB, или внешнее 5В.

В комплекте также идет программатор JTAG, Altera USB Blaster.

2. Среда Quartus II и наш первый проект

Для работы с данной ПЛИС нам нужно скачать официальную среду разработки - Quartus II Web Edition , она бесплатная. Заходим на официальный сайт http://dl.altera.com/15.0/?edition=web , на момент написания версия 15.0 самая новая, если вышла новее, скачиваем ее.

Выбираем:

Рис. 2 - выбираем необходимые продукты Altera

И жмем кнопку скачать (Download Selected Files). После чего нам предложат зарегистрироваться, регистрируемся, скачиваем и устанавливаем.

Создадим свой первый проект.

Запускаем Quartus, выбираем главное меню File -> New Project Wizard, появляется окно введения, жмем next. Далее нужно указать каталог для проекта и его имя, третье поля – имя верхнего модуля, попозже увидите, что это. Выбираем папку, куда хотим сохранить проект и придумываем имя, у меня test1.

Рис. 3 - окно мастра нового проекта

Жмем next, у нас спрашивают, пустой проект (empty project) или шаблон (Project template). Оставляем пустой, next. Дальше нас просят добавить существующие файлы, у нас ничего нет, поскольку мы только начинаем свой путь, жмем next.

Далее нам необходимо выбрать наш чип, это можно сделать в любое время. Выбираем как на рисунке, Family – Cyclone IV E, specific device selected in “Available devices” и выбираем наш чип EP4CE6E22C8N, он в самом начале. Если у вас другой, найдите свой, это важно . Жмем next.

Рис. 4 -

Появится окно - выбора средств проектирования, отладки, пока это пропускаем, нажимаем next и затем finish.

Рис. 5 - Окно

«

Assinments-Deice

»

В окне выбираем пункт «Unused pins». Эта настройка определяет, что будет с неподключенными пинами. Это может быть важно, в своем проекте вы вряд ли используете все пины, а не подключенные могут быть на деле соединены с землей или питанием (ну мало ли, кто разводил плату). Если вы подадите единичку на заземленный пин, то он сгорит, поэтому нужно внимательно следить за этим.

По умолчанию неиспользуемые пины «As input tri-stated with weak pull-up» (пины для ввода, находятся в третьем состоянии с высоким импедансом, со слабой подтяжкой по питанию), можно оставить или выбрать «As input tri-stated». Про подтягивающий резистор можете прочитать на википедии https://ru.wikipedia.org/wiki/Подтягивающий_резистор . В цифровой технике может быть три состояния, логическая единица – это напряжение питания или высокий уровень, логический ноль – это когда вывод подключен к земле или низкий уровень и высокоимпедансное состояние. Высокоимпедансное состояние - это когда пин имеет очень высокое сопротивление и практически не влияет на провод, к которому подключен, такое состояние нужно, например, при организации шин, когда множество устройств подключены к одному проводу и не активные устройства не мешают работе.

Рис. 6 - Окно

«

Device and Pin Options

»

, Unused Pins

Подключаем это все в «Assignment Editor»

Рис. 7 - Вызов

«

Assignment Editor

»

из меню или панели

В появившемся окне делаем как у меня, ну или если совсем правильно, то согласно схеме вашей платы.

Рис. 8 - Assinement Editor

В колонке «To» вписываем имя входа или выхода. В колонке «Assignment Name» выбираем «Location». В колонке «Value» номер контакта микросхемы, согласно схемы платы (у меня номера пинов написаны прямо на плате).

Также нужно указать, что делать с кнопками, которые одной ногой подключены к земле, а другой ко входу чипа. При нажатии на ноге будет низкий уровень, а вот без нажатия, непонятно, нога чипа будет просто висеть в воздухе, что очень плохо. Нужно подтянуть к питанию вход чипа либо резистором на плате, либо боле элегантным способом в «Assignments Editor». В колонке «Assignment Name» выбираем «Weak Pull Up resistor» для группы key* (группа обозначается через звездочку).

Рис. 9 - Assignment Editor

Далее нужно создать описание модуля верхнего уровня, который будет работать непосредственно с ножками чипа, все остальные модули будут работать только с ним. В главном меню жмем New, и выбираем "Design Files-> Block Diagram/Schematic File".

Рис. 10 - Диалог новых файлов

В открывшемся окне выбираем инструмент «Pin Tool» и располагаем вход и выход (пины ввода и вывода) на диаграмме. Переименовываем вход как key, выход как led и соединяем их проводником. Сохраняем и нажимаем "Start Compilation".

Рис. 11 - Окно графического описания, выделены Pin Tool и Start Compilation

После компиляции у нас возникли предупреждения, пока игнорируем их, они касаются неподключенных пинов, отсутствия тактового сигнала и описания для «Timing Analyzer».

Подключаем демоплату и программатор, выбираем инструмент «Programmer». В окне должно значиться «USB-Blaster », если нет то нажимаем «Hardware Setup» и пытаемся разобраться почему нет, скорее всего не установлены драйвера, смотрим в устройства Windows, ищем неопределенные устройства, может с кабелем проблема. Если все хорошо нажимаем «Auto Detect» и выбираем наш чип.

Рис. 12 - Окно Programmer

Нажимаем двойным щелчком мыши в поле «File» и выбираем файл для записи на ПЛИС (находиться в папке output_files нашего проекта), ставим галочку в поле «Program / Configure», и нажимаем кнопку «Start».

Рис. 13 - Окно Programmer, наш чип уже сконфигурирован

Поздравляю с первой конфигурацией ПЛИС! Диод D1 должен светиться, при нажатии key1 должен гаснуть (так как кнопка замыкает ножку с землей), далее мы с этим что-нибудь сделаем)

(C) Research/VolgaSoft Современные технологии. ALTERA. (ознакомительный материальчик) ВСТУПЛЕНИЕ В этой статье пойдет речь о совре- менном маленьком чуде, о расчитанном прорыве в мире цифровой электроники - микросхемах программируемой логики. Это тот кирпичик, который стоит в самых сов- ременных моделях ZX-SPECTRUM - GMX и СПРИНТЕР , это та самая микросхемина, на которой можно сделать почти все - от Z80X (допустим, 30мгц, машинный цикл 1 такт), до всего Пентагона вместе с 2D акселератором, GSкой, мышью и IDE конт- роллером. Наверное каждый радиолюбитель раз- рабатывая цифровое устройство, в душе мечтал - где бы найти таблетку от всех болезней - микросхему, которая заменит все. Инженеры особенно нуждались в подо- бных устройствах, так как при разработке серьезного изделия приходилось проекти- ровать заказную интегральную схему "под задачу". От момента вычерчивания логики, до появления рабочего изделия проходило как правило несколько месяцев и затрачи- валось огромное количество ресурсов. Но спрос рождает предложение - появились полузаказные большие интегральные схемы (БИС) и программируемые логические мат- рицы (ПЛМ). Наука не стояла на месте, техноло- гии становились все более и более совер- шенными, и однажды был анонсирован выход пакета "софт"+"железо"+"камень". Задумка была очень простой: разработчик рисует в софте схему (может переносит ее с бума- ги), или описывает логику будущего изде- лия двоичными уравнениями и простыми операторами, затем компилятор переводит схему в некий код, а код зашивается про- грамматором ("железо") в микросхему про- граммируемой логики ("камень"), которую можно сразу же впаивать в плату. И ника- ких затрат на разработку кристалла, и испытания. Разработчики цифровых уст- ройств подхватили "на ура" новинку. На сегодня на рынке масса призводи- телей БИС программируемой a логики (ПЛ). Их продукты отличаются a как емкостью и архитектурой, a так и качеством софта и аппаратной поддержки, сервисом и в конце концов стоимостью. Явным лидером сегодня является фир- ма Altera Corporation . Она завоевала рынок благодоря не только широкому спек- тру изделий, но и грамотному распростра- нению своей продукции. Например, пользо- вание софтпродукцией (студенческие вер- сии) с целью обучения - бесплатно. Для России в общем-то не принципиально (у нас почти никто в глаза не видал закон об авторском праве), а вот за границей этот вопрос актуален. К тому-же продук- ция фирмы буквально вломилась на отечес- твенный рынок - в результате мы теперь почти все сидим на ней. ОТ СЛОВ - К ДЕЛУ СБИС ПЛ фирмы Altera классифицирую- тся по следующим признакам: 1) степень интеграции (количество доступных вентилей (элементов 2И-НЕ) и триггеров); 2) архитектура простейшего функцио- нального преобразователя (ячейки); 3) организация внутренней структуры СБИС и структуры матрицы соеденений фун- кциональных преобразователей (метод сое- динения ячеек); 4) наличие внутренней RAM памяти; 5) технологии изготовления програм- мируемого элемента (Fuse, EPROM, EEPROM, FLASH, SRAM) - то, каким образом зашита схема. Для работы с большинством своих БИС ПЛ фирма Altera предлагает язык описания аппаратуры MAX+plus II. В системе автоматизации проектиро- вания MAX+plus II поддержано шесть се- мейств СБИС ПЛ. ┌─────────┬──────────────────────┐ │ │ Параметры │ │ ├──────────┬─────┬─────┤ │Семейство│Логическая│UPin │Tech │ │ │ емкость │ │ │ │ │ │ │ │ ├─────────┼──────────┼─────┼─────┤ │Classic │ 300-900 │22-64│EPROM│ │MAX5000 │ 600-3750 │24-84│EPROM│ │MAX7000E │ 600-5000 │до164│EEP- │ │MAX9000 │ 6e3-12e3 │до216│ROM │ │FLEX8000A│ 2500-16e3│до208│SRAM │ │FLEX10K │ 1e4-1e5 │до406│SRAM │ └─────────┴──────────┴─────┴─────┘ Логическая емкость - число доступ- ных элементов 2И-НЕ, то есть в FLEX10K влезет до 25000 наших ЛА3-их. UPin - число пользовательских выво- дов. Tech - технология. Практическое пояснение к таблице: допустим берем самый дохлый FLEX8000A (техноглогия SRAM - т.е. после включения питания схемку ус тройства надо "залить" в альтерину), вешаем пользовательскими ногами на шину родимиго Спекки (при этом останется несколько свободных), делаем элементарный дешифратор порта на россыпи и сцепляем его со входом альтерины. Что мы получаем? Мы получаем супер устройст- во!!! Ведь теперь можно вливать в альте- ру фактически любую схему!!! Это может быть что угодно от внешнего мат. процес- сора (допустим в один порт побайтно ло- жим 16-битное число, в другой - второе число, еще куда-нибудь - код операции, затем снимаем результат), до всего, что уму постижимо (если ткнуть несколько свободных ног "куда следует" - можно сделать аппаратную заливку и аппаратное построение отрезков, многоканальные про- граммируемые прерывания (особенно актуа- льно для цифрового звука), новые комман- ды процессора (как в "спринтере" или до- полнительные регистры процессора....). Можно наделать библиотек аппаратных фун- кций чтобы не изобретать велик, как это до сих пор делают упрямые "кодеры" и считывать их в соответствии с задачей. "Прошивка" схемы того же FLEX8282A ("са- мый дохлый", см. выше) весит, если мне не изменяет память, 6кБ. Во время конфи- гурирования все пользовательские ноги находятся в Z-состоянии и не влияют на работу системы. Если нужно сделать уст- ройство "на века" и не конфигурировать его каждый раз после включения - можно использовать семейство MAX. Так же неко- торые БИС семейства МАХ имеют защиту от "сливания схемы" - бит секретности раз- работки, однако, на мой взгляд, примене- ние этого семейства несколько ограничено (по крайней мере в "домашних" условиях) из-за необходимости в программаторе и ограниченом количестве циклов программи- рования. ТЕПЕРЬ ПАРА СЛОВ О СРЕДЕ РАЗРАБОТ- КИ: ЯЗЫКЕ ОПИСАНИЯ АППАРАТУРЫ MAX + PLUS II. Система MAX + plus II написана под следующие платформы: PC , MAC , SUN . Ни Спекки , ни прeсловутой подружки в этом списке почему-то не оказалось. Система очень добрая, простая и с широкими воз- можностями. Основными компонентами яв- ляются графический и текстовый редакто- ры, компилятор, редактор диаграмм (он же "дебуггер"), таймер, редактор размещения и разводки. В графическом редакторе рисуется схема устройства (если использовано гра- фическое задание). В качестве элементов схемы можно задействовать логику "по бу- ржуйскому госту", есть там и вся 74 се- рия, а если не нравятся вражеские обоз- начения - можно нарисовать все по-нашин- ски и заставить работать. Текстовый редактор используется для текстового описания аппаратуры. Язык что-то среднее между dBase , C , Pas- cal . Есть чуть ли не готовая комманда описания синхронного конечного автомата, есть и if и case . Сумматор описывается буквально как C=A+B . А телефонная чип-карта описывается и тестируется (см. ниже) за часик не напрягаясь. Компилятор проверяет схемку (или текстик) и генерирует прошивку под зада- нный "кирпич". Широко регулируемые пре- делы оптимизации по скорости и объему позволяют выжать из устройства максимум быстродействия или минимум занимаемой площади на кристалле. Есть полезная вещь дизайн доктор. Показывает где есть гонки и опасные места, и при каких условиях они появятся, не забывает попросить на- жать сброс для инициализации устройства после включения и т.д. В редакторе диаграмм можно промоде- лировать работу будущего устройства: до- пустим задать входные сигналы и посмот- реть соотвествующие им выходные, гонки тоже не забывают отображаться. Поэтому прежде чем собирать схему лучше прогнать ее в "максе" и проверить. Правда нашелся и глючечек - не завелся Т-триггер сдела- нный из RS , сихронизируемого перепадом, хотя на практике он пахал. Просмотр диа- грамм сделан очень удобно: можно смот- реть диаграммы, объединив их в группы и представив удобную для просмотра систему исчисления (двоичную, десятичную, шест- надцатиричную). Входные данные можно за- давать в том числе и кодом Грея . Можно посмотреть и внутренние состояния авто- мата. Таймер - он и в африке таймер - по- казывает задержки и максимально возмож- ную рабочую частоту устройства. Редактор размещения и разводки ис- пользуется для "аппаратного" убирания гонок (перестановки логических ячеек) и расстановки пользовательских выводов. Прайс дистрибьтера фирмы Altera я к величайшему несчастью потерял, посему скажу лишь по памяти, что FLEX10K10 стоит от $20, FLEX8282A от $8, элементы семейства MAX стоят от $3.3. Если инте- ресно, где можно добыть информацию, мо- жете пролистать до конца статьи, ибо да- лее пойдет справочная информация. БОЛЕЕ ПОДРОБНАЯ ИНФОРМАЦИЯ О СЕМЕЙСТВАХ Семейство Classic объединяет 3 се- рии СБИС. БИС этого семейства позволяют заменить устройство, содержащее от 10 до 20 микросхем средней степени интеграции, и обеспечивают: * задерку распространения сигнала от любого входа да выхода БИС не более 10 нс; * устойчивую работу на частотах до 100 МГц; * возможность работать в режиме по- ниженного энергопотребления; * возможность задания режима секре- тности разработки (из микрухи схему на- зад не слить). Прим.: похоже уже сняты с производ- ства. Семейство MAX5000 объединяет 5 се- рий СБИС. БИС этого семейства позволяют заменить устройство, содержащее до нес- кольких десятков микросхем средней сте- пени интеграции, и обеспечивают: * задерку распространения сигнала от любого входа да выхода БИС не более 15 нс; * устойчивую работу на частотах до 76 МГц; * возможность задания режима секре- тности разработки; * возможность использования трех режимов работы выходных буферов: вход, выход, двунаправленный. Семейство MAX7000 объединяет 7 се- рий СБИС. БИС этого семейства позволяют заменить устройство, содержащее до сотни микросхем средней степени интеграции, и обеспечивают: * задержку распространения сигнала от любого входа дo выхода БИС не более 5 нс; * устойчивую работу на частотах до 178 МГц; * возможность регулирования скорос- ти переключения выходных буферов; * возможность использования 4-х ре- жимов работы выходных буферов: вход, вы- ход, двунаправленный, открытый коллек- тор; * возможность задания режима пони- женного энергопотребления как для всей СБИС в целом, так и для цепей распрост- ранения отдельных сигналов; * возможность программирования и репрограммирования после распайки на плате; * возможность задания режима секре- тности разработки; * работу с пониженным (3.3 В) нап- ряжением питания. Прим.: ряд серий соответствует ста- ндарту шины PCI. Семейство FLEX8000A объединяет 7 серий СБИС. БИС этого семейства позво- ляют заменить устройство, занимающее де- сятки плат, выполненных на микросхемах средней степени интеграции, и обеспечи- вают возможность: * устойчивой работы на частотах до 294 МГц; * эмуляции внутренней шины с 3мя состояниями; * работы с пониженным (3.3 В) нап- ряжением питания; * работы в системах со смешанным (3.3 В, 5 В) напряжением питания; * реализации неограниченного числа циклов конфигурирования, в том числе и "на лету", т.е. без выключения питания СБИС; * регулирования скорости переключе- ния выходных буферов; * возможность использования 3-х ре- жимов работы выходных буферов: вход, вы- ход, двунаправленный. Прим.: все СБИС этой серии соответ- ствует стандарту шины PCI. Семейство MAX9000 объединяет 4 се- рий микросхем. БИС этого семейства поз- воляют заменить устройство, занимающее десятки плат, выполненных на микросхемах средней степени интеграции и обеспечи- вают возможность: * устойчивую работу на частотах до 125 МГц; * независимого использования логи- ческой части и триггера макроячейки; * возможность задания режима пони- женного энергопотребления как для всей СБИС в целом, так и для цепей распрост- ранения отдельных сигналов; * возможность программирования и репрограммирования после распайки на плате; * работы в системах со смешанным (3.3 В, 5 В) напряжением питания; * регулирования скорости переключе- ния выходных буферов; * использование 3-х режимов работы выходных буферов: вход, выход, двунапра- вленный. Прим.: ряд серий соответствует ста- ндарту шины PCI. Семейство FLEX10K объединяет 7 се- рий СБИС. БИС этого семейства позволяют заменить устройство, занимающее сотни плат, выполненных на микросхемах средней степени интеграции, и обеспечивают воз- можность: * устойчивой работы на частотах до 450 Мгц; * реализации на кристалле статичес- кой памяти и ПЗУ объемом до 24Кбит; * независимого использования логи- ческой части и триггера кадого логичес- кого элемента; * эмуляции внутренней шины с 3мя состояниями; * умножения внутренней тактовой ча- стоты; * работы в системах со смешанным (3.3 В, 5 В) напряжением питания; * реализации неограниченного числа циклов конфигурирования, в том числе и "на лету", т.е. без выключения питания СБИС; * регулирования скорости переключе- ния выходных буферов; * возможность использования 4-х ре- жимов работы выходных буферов: вход, вы- ход, двунаправленный, открытый коллек- тор. Прим.: все СБИС этой серии соответ- ствует стандарту шины PCI. Вот такие дела. Добавлю лишь, что прогресс не стоит на месте и в каждом семействе серий поприбавилось. ЯВКИ WWW.ALTERA.COM - там можно получить более подробную информацию и электронные ключи к программе MAX + Plus II (прики- нувшись студентом или научным работни- ком). Фирма ЭФО. E-mail: [email protected] Тел. (812) 247-5340 194021 Санкт-Петербург, Политехническая ул.,21 (здесь можно купить соответсвующие элементы). ЛИТЕРАТУРА 1. Обзор элементной базы фирмы ALTERA (Антонов А.П., Мелехин В.Ф., Филлипов А.С.; СПб 1997) 2. Эта же книга (только кажется по больше) лежит на компакте с MAX + Plus II в виде.PDF (кажись 45 МБ), правда на английском.

Программируемые логические интегральные схемы фирмы ALTERA и система автоматизированного проектирования MAX+PLUS II

Программируемые логические интегральные схемы (ПЛИС), а в зарубежной литературе именуемые PLD (programmable logic devices), - это полу заказные цифровые БИС, которые благодаря архитектурным и технологическим особенностям можно разрабатывать и изготовлять без специализированного технического оборудования. ПЛИС появились на мировом рынке в середине 80-х гг. И сразу получили широкое распространение, переместив процесс создания специализированной БИС с завода на рабочее место проектировщика. Цикл разработки БИС сократился до нескольких часов, и значительно уменьшились соответствующие затраты.

С начала 90-х гг. наибольшим спросом пользуются ПЛИС, обладающие:

высокой логической интеграцией на основе технологий КМОП;

быстродействием до 80 -100 МГц и выше;

возможностью программирования (загрузки внутренней конфигурации) без программатора.

Всем этим требованиям соответствуют ПЛИС фирмы ALTERA (США) - мирового лидера в области ПЛИС. В настоящее время ALTERA выпускает семь семейств ПЛИС различной архитектуры [ 14 ].

В России наиболее известны ПЛИС классического (Classic) семейства, некоторое время выпускаемые компанией INTEL. Основными преимуществами этих микросхем являются простота, низкая стоимость, удобные для монтажа DIP- корпуса, микропотребление энергии в статическом режиме и возможность поддержки отечественными средствами (САПР “ФОРС+” , программаторы “Блиц”, ”Стерх”, ”Форсис”). ПЛИС ЕР220 заменяет любую микросхему серии 1556 (ХП4, ХП6, ХП8, ХЛ8) .

Все ПЛИС изготавливаются по технологии КМОП с ультрафиолетовым стиранием (EPROM), обеспечивающей следующие параметры энергопотребления:

в статическом режиме - 10-30 мкА;

на частоте 1 МГц - 2-8 мА;

при увеличении тактовой частоты - 1 мА/МГц.

Для снижения цены на 30-40% при серийном производстве изделий все ПЛИС также выпускаются в пластмассовых корпусах (DIP и PLCC) с однократным программированием.

Недостатками ПЛИС классического семейства являются относительно невысокая степень интеграции и некоторые особенности архитектуры: отсутствие у триггеров входа установки в “1” (SET), блокирование контактов при реализации внутренних элементов памяти.

Этих недостатков полностью лишены ПЛИС семейств MAX7000 и FLASHlogic, которые имеют матричную архитектуру, т.е. содержат программируемые матрицы логических вентилей “И”, ”ИЛИ” и триггеры.

Семейство MAX7000 состоит из семи микросхем со степенью интеграции от 1200 до 10000 эквивалентных логических вентилей, содержащих от 32 (EPM7032) до 256 (EPM 7256) триггеров.

Дополнительно выпускается ПЛИС EPM7032V - функциональный аналог микросхемы EPM7032 с напряжением питания 3,3 В.

ПЛИС семейства MAX7000 изготавливаются по технологии КМОП с электрическим стиранием (EEPROM). Они обеспечивают:

минимальную задержку распространения сигнала от входа до выхода 5 нс.;

максимальную тактовую частоту 190 МГц;

до 100 циклов программирования/стирания.

ПЛИС семейства MAX7000 имеют гибкую архитектуру. Их макроячейки содержат по две независимые линии обратной связи; с триггера и с контакта. Это позволяет использовать триггер в качестве внутреннего регистра, а контакт одновременно - как входной порт. Дополнительными ресурсами ПЛИС являются термы расширения (expander terms) - конъюнкторы, инверсные выходы которых образуют обратные связи с матрицей элементов “И”. Термы позволяют формировать управляющие сигналы (например, CLK, SET, RESET) без затрат макроячеек. В результате перераспределения термов между макроячейками число входов элементов “ИЛИ” может быть увеличено до 32.

Каждая макроячейка имеет индивидуальный турбо бит, программирование которого позволяет уменьшить потребляемую мощность при некотором снижении быстродействия. Начиная с 1996 г. все ПЛИС семейства MAX7000 будут выпускаться в варианте ISP (in system programmable - программируемые в системе). Это позволит программировать и стирать схему непосредственно на рабочей плате через 4-й сигнальный интерфейс, подключенный к порту компьютера. Наличие программатора становится необязательным, что значительно упрощает и удешевляет применение ПЛИС.

ПЛИС семейства MAX7000 имеют низкую стоимость. Например, цена микросхемы ЕРМ7032 составляет менее 7 , а микросхемы ЕРМ7128 - менее 25.

С появлением семейства MAX7000 значительно уменьшилась практическая ценность выпускавшихся ранее ПЛИС семейства MAX5000, т.к. появились аналоги всех микросхем (например, ЕРМ5128 - ЕРМ7128) с лучшими характеристиками быстродействия и энергопотребления по более низким ценам.

MAX+PLUS II - это система автоматического проектирования программируемых логических интегральных схем (ПЛИС), разработанная Altera Corporation, мировым лидером по производству ПЛИС.

MAX+PLUS II - это многофункциональный программный продукт, обеспечивающий проектировщику возможность полного проектирования ПЛИС, начиная с ввода схемы, которую проектировщик собирается реализовать на ПЛИС и заканчивая программирования самой ПЛИС на программаторе.

MAX+PLUS II предлагает следующие возможности для пользователя:

ввод внутренней структуры ПЛИС путем графического ввода функциональной схемы;

ввод внутренней структуры ПЛИС c помощью языка программирования высокого уровня Altera Hardware Description Language (AHDL), который полностью встроен в оболочку MAX+PLUS II ;

моделирование работы ПЛИС в виде временных диаграмм;

при наличии программатора произвести запись спроектированной структуры в ПЛИС и др.

При описании внутренней структуры ПЛИС с помощью AHDL возможны несколько вариантов.

В первом варианте проводить описание структуры в примитивах, т.е. используя простейшие функции типа RS-триггер,D-триггер, T-триггер, JK-триггер и др.

При втором варианте проводить описание при помощи примитивов и мега-функций.

Мега-функции представляют собой сложные логические функции типа счетчик, мультиплексор, дешифратор, регистр и др.

Преимуществом первого варианта является то, что транслятор затрачивает меньше времени на преобразование простейших функций языка AHDL в машинные коды.

Недостатками данного варианта является большой объем текста программ и необходимость подробного описания всей системы.

Во втором варианте, при использовании мега-функций, отпадает надобность подробного описания элементов в том смысле, что программист задает только параметры сложной логической функции. Для примера, используя мега-функцию lpm_counter счетчик можно описать, задав только тактируемый вход и ширину самого счетчика. Это значительно уменьшает объем, занимаемый текстом программы, а также позволяет несколько сократить время написания программы.

Недостатком является то, что на трансляцию программы в машинные коды затрачивается больше времени по сравнению с первым вариантом.

Но в конечном итоге результат получается одинаковым, поэтому стиль написания программного продукта целиком зависит от проектировщика.

При отладке написанного программного продукта SIMULATOR MAX+PLUS II позволяет подробно рассмотреть результат работы ПЛИС в виде временных диаграмм. Проектировщик может выбирать различные выходы и промежуточные состояния, описанные в программе, а также задавать различные входные воздействия.

Первая фирма, вышедшая на рынок с программируемыми интегральными микросхемами (ПЛИС). Фирма Altera предлагает два САПР MAX+PLUS II и Quartus II. Каждый САПР поддерживает все этапы проектирования: Ввод проекта, Компиляция, Верификация и Программирование. Каждый САПР имеет Tutorial (Самоучитель), который устанавливается при инсталяции пакета. Tutorial состоит из занятий, в ходе которых проходится весь цикл проектирования от ввода проекта до программирования микросхем. При инсталяции также устанавливаюся файлы, описывающие проект так, что в ходе изучения Tutorial можно пропускать отдельные занятия и использовать готовые файлы. Например, можно пропустить "Ввод проекта" и перейти к "Компиляции" проекта, используя готовые файлы.

Система MAX+PLUSII имеет эффективные алгоритмы синтеза, позволяющие максимально использовать ресурсы кристалла и большой набор инструментов для верификации устройств на функциональном и временном уровне проектирования.

Фирма также распространяет специализированные комплекты Design Kit, облегчающие применение ПЛИС в конкретных задачах. Такие комплекты содержат логические функции, совместимые с САПР и методологию их использования. Интерес представляют Design Kit, посвященные разработке изделий в стандарте шины PCI и схем цифровой обработки сигналов. Первый включает в себя функции-шаблоны для реализации контроллеров (Master/Slave) и схемы проверки паритета. Второй ориентирован на эффективную реализацию таких схем, как умножители, КИХ-фильтры, операции с плавающей точкой, преобразования Фурье, Рида-Соломона и т.д.

МАХ ориентирован на сопряжение со стандартами VHDL, EDIF, Verilog. Любая конфигурация САПР импортирует входные данные в формате EDIF и формирует результаты проектирования во всех перечисленных форматах. С помощью программ-трансляторов возможен импорт информации в формат текстового описания САПР МАХ из файлов в форматах PDS (САПР PLDShell, PALASM) и XNF (САПР XACT фирмы Xilinx). Имеется возможность конвертации схем, созданных в системе OrCAD, в файлы в формате собственного графического редактора.

Фирма Altera предлагает бесплатные версии САПР MAX+PLUS II BASELINE и Quartus II Web Edition, которые поддерживают все этапы проектирования от ввода проекта до программирования. Ограничениями являются количество поддерживаемых микросхем и некоторые функции для Quartus II. Бесплатные версии САПР можно скачать с сайта фирмы Altera (https://www.altera.com/support/software/download/sof-download_center.html).